基于国产软硬件系统的实验教学FPGA仿真工具设计

王建新,肖超恩,张磊,孙猛,韩英,许弘可

(北京电子科技学院电子与通信工程系,北京 100070)

目前,我国高等教育正处于内涵发展的关键时期和全面提高人才培养能力、建设教育强国的关键阶段[1-2]。实验教学应着力于新工科建设与发展,在EDA领域,如何提高相关仿真工具软件的自主化程度,提升学生解决复杂工程问题的能力,是我们面临的一个重要问题[3-4]。

可编程门阵列(Field Programmable Gate Array,FPGA)可通过编程方式组合成任意数字电路,广泛应用于电子、通信、计算机、人工智能等领域。FPGA 作为专用集成电路领域中的一种半定制电路,既解决了定制电路功能单一,又克服了通用处理器计算效率低下的问题。硬件描述语言将硬件设计软件化,软件设计虚拟化,以大规模可编程逻辑器件为设计载体,以软件设计为基础,结合仿真综合,完成对FPGA芯片的编译、布局布线、逻辑映射和下载工作[5-6]。

目前,FPGA 集成开发工具在Windows 操作系统(某些Linux操作系统)和X86 平台下能够完美运行,其集成开发工具主要包括:国外的Quartus Ⅱ、Vivado、Diamond等;

国产FPGA 开发工具主要包括:Pango、TangDynasty、云源软件、HqFpga、FX 伏羲软件、Supra软件等[7-8]。

在代码仿真方面,主要软件包括:Modelsim、NCVerilog、NC-VHDL、NC-SIM等付费软件[9-10],目前不支持国产操作系统及国产CPU,主要用于大型芯片或设备开发、生产测试环境,且使用受限,授权价格昂贵,在高校FPGA实验教学环境建设和国产化方面存在一定问题。为便于实验教学,基于Linux 操作系统下的开源软件开发工具Gambas设计并实现了基于国产操作系统和国产CPU的FPGA 仿真工具EasyVerilog,针对不同架构CPU的不同指令集问题,集成并适配了相关开源插件,可实现Verilog 代码编写、编译、仿真、综合等相关功能,可用于数字电子技术、EDA、FPGA 等相关实验课程的数字逻辑设计与仿真,在一定程度上降低了实验教学中对如ModelSim等国外EDA仿真工具软件的依赖。

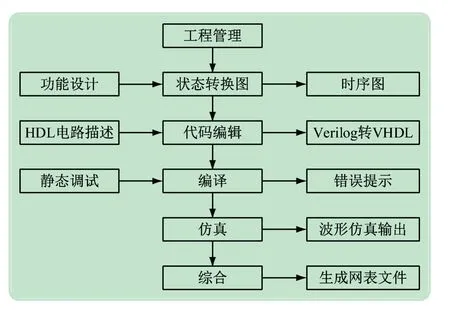

本文采用Gambas 进行FPGA 集成开发工具EasyVerilog的设计与实现[11-13],主要工作包括:工程管理,代码编辑,Verilog 代码的编译、仿真、综合,Verilog转VHDL,代码模板,系统升级、时序图和状态转移图绘制等功能,系统架构如图1 所示。

图1 系统架构

该仿真工具可运行于Deepin、UOS、银河麒麟、优麒麟、Loongnix等国产操作系统,以及龙芯、飞腾、鲲鹏、兆芯等国产CPU,可用于FPGA硬件逻辑设计中轻量级Verilog代码编写、编译、仿真与综合。

2.1 Gambas开发工具

Gambas是一套基于类Unix 操作系统的开源程序设计工具。Gambas以可视化为主要特点,采用面向对象、事件驱动机制,把Linux程序设计的复杂性封装起来,使研究和开发Linux 环境下的应用程序变得简单易行。实际上,Gambas可以看作是具有对象扩展功能的BASIC解释器,使用BASIC 和C 混合语法规则,在体系结构上参考Java实现方案,界面实现上采用Qt4、Qt5、GTK +2、GTK +3 兼容方案[14-16]。用Gambas 开发的应用程序是一组文件的集合,每个文件描述一个类,类文件编译后由解释器执行。

2.2 系统实现

2.2.1 工程管理

EasyVerilog集成开发工具窗体的左侧设计了一个工程管理窗口,以树状列表形式列出了当前工程中的Verilog代码和Testbench 文件等,采用TreeView 控件实现,开发工具窗口如图2 所示。

图2 开发工具窗口

可通过“文件”菜单下“新建”中的“工程文件”菜单新建一个工程,也可以在“打开”菜单下打开一个已经存在的工程,如图3 所示。当点击左侧区域的工程管理窗口中相关文件时,会在中间区域的代码编辑窗口显示Verilog 代码或Testbench 文件,右侧为代码缩略图窗口,最下侧为控制台窗口。

图3 “文件”菜单

2.2.2 代码编辑

代码编辑窗口实现源代码编辑功能,用来编写和编辑Verilog代码。主要包括撤消、恢复、剪切、复制、粘贴、删除、全选、查找和转到等文本操作功能,采用TextEditor控件实现,与主流代码编辑器风格保持一致。使用查找功能时,会在底部出现一个文本框,输入要查找的文本,代码编辑窗口中的相关文本会高亮显示,使用Highlight属性实现,如图4 所示。

图4 “编辑”菜单

2.2.3 编译

EasyVerilog开发工具采用插件(Plugin)技术实现快速开发。在编译、仿真和综合阶段,设计了一种通用插件接口方案,借鉴Qt 中信号(Signal)与槽(Slot)的通信机制,通过类回调(函数)形式进行“隐式”连接,“显示”收发数据,在操作系统中以流(Stream)的形式向插件发送相关命令(Command),插件接收到命令后返回相关计算结果(Result)到流,系统再以过程(Process)方式将结果截获并回显。该方案有利于系统功能扩展、升级与整体迁移。

Verilog代码编译采用了Icarus Verilog(iverilog)开源插件,由Stephen Williams 开发,也可配置其他编译插件。Icarus Verilog 能将符合IEEE-1364 格式的Verilog 代码编译为指定格式,当前支持IEEE Std 1364-2005。Icarus Verilog 通过下载源码并进行本地编译形式,仅需要进行少量配置文件和接口代码修改,可通过一次代码编写,指定平台编译的形式支持所有的国产操作系统和国产CPU,包括最新的龙芯LoongArch指令集。通过iverilog 命令编译Verilog 代码,如果出错,会在最下侧的控制台窗口输出相关错误信息,如果无误,则根据代码要求输出相关信息。“工程”菜单提供了“编译当前文件”“编译全部”“仿真”“综合”和“Verilog转VHDL”等功能,如图5 所示。

图5 “工程”菜单

2.2.4 仿真

Verilog代码编译完成后,通过vvp 命令生成波形文件,使用GTKWave 插件显示波形。GTKWave 是一个功能齐全的波形查看工具,可读取LXT、LXT2、VZT、FST和GHW文件以及标准Verilog VCD/EVCD文件。

2.2.5 综合

Verilog代码综合采用yosys插件。yosys是一款开源FPGA 综合工具,支持Verilog-2005,并为各应用领域提供了一套基础综合算法,主要特性包括:可将Verilog转换为BLIF、EDIF、BTOR、SMT-LIB 和simple RTL Verilog 等格式;

可进行属性和等价性检查,逻辑化简和优化;

可映射到ASIC 标准单元库;

可映射到Xilinx 7 系列和Lattice iCE40、ECP5 等FPGA;

自定义综合流程、扩展自定义综合算法、扩展针对其他FPGA的综合等。

由于综合需要大量命令行操作,EasyVerilog 采用内置命令行输出与虚拟终端设计方法,有效避免与其他终端的干扰与数据阻塞,实现一个与终端并行执行的虚拟终端系统来模拟终端,通过命令缓冲批处理形式依次发送相关综合操作命令到虚拟终端,并将执行结果回馈,提高了运行效率。

2.2.6 绘制时序图

在Verilog代码编写前,可能需要对所设计的硬件逻辑功能进行全面、深入的分析,此时需要列出相关控制信号并按需绘制状态转移图或(和)时序图。EasyVerilog开发工具集成了网页版本的状态转移图绘制工具SequenceDiagrams 和时序图绘制工具WaveDromEditor。该功能放置在“工具”菜单中。此外,“工具”菜单可插入Verilog 代码的相关模板,如时序逻辑、组合逻辑等代码模板框架,可打开并浏览当前工程文件夹,安装与升级插件,并设计有一个文本计算器,如图6 所示。

图6 “工具”菜单

通过一个实例来说明利用该集成开发工具实现Verilog数字逻辑设计的基本步骤和技巧。例如:实现一个4 bit计数器,并进行编译、仿真、综合。

(1)功能设计。编写一个4 bit计数器实例,当系统复位时计数器清零,否则进行累加操作。采用WaveDromEditor设计并编辑时序图,如图7 所示。

图7 计数器时序图

(2)Verilog HDL 硬件描述。在代码编辑窗口中编写Verilog代码,描述硬件逻辑功能,包括两类基本模块(module),即功能模块和测试模块(Testbench),文件名分别为counter.v 和counter_tb.v,4 bit 计数器功能模块代码为:

(3)编译与仿真。当选择“工程”菜单中的“编译当前文件”时,可编译当前的功能模块,当选择“编译全部”时,则可编译该工程中所有功能模块和测试模块。当全部模块编译无误后,选择“仿真”,即可生成波形文件,并调用GTKWave 插件显示仿真波形,如图8 所示。

图8 计数器仿真波形

(4)综合。对功能模块进行综合,生成网表文件并以图形方式显示,在虚拟终端显示输出信息,如图9、10 所示。

图9 网表文件

本文设计了一个轻量级,支持国产操作系统和国产CPU的FPGA仿真工具EasyVerilog。经过测试,运行时内存占用约为20 MB,不含插件安装程序约为100 KB,包含插件完全安装约为500 MB,适合于目前国产计算设备软硬件资源少,需要对Verilog 代码逻辑进行仿真的场合,适用于轻量级科研仿真、实验教学等场景。目前,该系统已经应用于数字系统设计、专业实习、电子电路课程设计等相关课程的实验教学,经相关实验课程的反复测试验证与使用,结果表明:该系统能够在龙芯派二代2K1000 +Loongnix 操作系统以及树莓派等单板计算机上流畅运行,也可在FT2000 +银河麒麟、龙芯3A4000 +UOS国产计算机上完美运行。同时,支持在国产X86 平台+各类国产操作系统运行,在教学上能做到对FPGA代码编辑和编译工具的替代和ModelSim仿真工具的部分替代,并且可为后续开发提供理论基础与技术支持。

图10 图形显示及虚拟终端

猜你喜欢 插件菜单代码 中国新年菜单疯狂英语·新悦读(2020年1期)2020-02-20自编插件完善App Inventor与乐高机器人通信电子制作(2019年22期)2020-01-14创世代码动漫星空(2018年11期)2018-10-26创世代码动漫星空(2018年2期)2018-10-26创世代码动漫星空(2018年9期)2018-10-26创世代码动漫星空(2018年5期)2018-10-26基于jQUerY的自定义插件开发软件(2016年6期)2017-02-06本月菜单美食堂(2017年1期)2017-01-13基于Revit MEP的插件制作探讨智能建筑电气技术(2015年1期)2015-03-01一个“公海龟”的求偶菜单鸭绿江(2013年10期)2013-03-11栏目最新:

- 2024年度在理论学习中心组关于群众路线...2024-01-16

- 在退役军人事务工作领导小组会议上讲话...2024-01-15

- 中秋国庆队伍教育管理工作动员部署会议...2024-01-15

- 2024年度区委书记在文旅农康融合发展大...2024-01-14

- 医院纪检监察干部队伍教育整顿个人党性...2024-01-14

- 教师演讲稿:牢记育人使命,涵养高尚师德...2024-01-13

- 2024年组织部长在市委理论学习中心组专...2024-01-13

- 2024年区人民法院案件质量评查办法(2篇...2024-01-13

- 2024年区长在指导某街道干部作风建设动...2024-01-11

- 在公司成立周年大会上讲话(3篇)(完整...2024-01-10

相关文章: